Revision 1 to Document 11/32-E 14 April 1998 Original: English

Source: Document 11/32

# **Study Group 11**

#### DRAFT REVISION OF RECOMMENDATION ITU-R BT.1120-1

# DIGITAL INTERFACES FOR 1125/60<del>/2:1</del> AND 1250/50<del>/2:1</del> HDTV STUDIO SIGNALS

(Question ITU-R 65/11)

(1994-1998)

The ITU Radiocommunication Assembly,

considering

- a) that in the scope of Recommendation ITU-R BT.709, studio standards for HDTV have been developed for 1125/60 and 1250/50, which contain systems related to conventional television and systems with square pixel common image format including progressive scanning;

- b) that Recommendation ITU-R BT.1200 specifies a flexible system description based on the carriage of declarable parameter values;

- e) that there exist signal specifications for HDTV studio systems based on 1125 lines, 60 Hz field rate, 2:1 interlace and 1250 lines, 50 Hz field rate, 2:1 interlace, based on the above Recommendations;

- d) that a whole range of equipment based on the above systems has been developed and is commercially available, including all those necessary for broadcasting chains and for industrial applications;

- b) that Recommendation ITU-R BT. 709 contains following HDTV studio standards;

For 2:1 Interlace scanning and related to conventional television systems;

1125 Total line, 2:1 Interlace scanning, 60-field/sec, 1035 Active line standard

1250 Total line, 2:1 Interlace scanning, 50-field/sec, 1152 Active line standard

For 2:1 Interlace scanning and Common Image Format (1080 x1920);

1125 Total line, 2:1 Interlace scanning, 60-field/sec, 1080 Active line standard

1250 Total line, 2:1 Interlace scanning, 50-field/sec, 1080 Active line standard

For 1:1 Progressive scanning and Common Image Format (1080 x 1920);

1125 line, 1:1 Progressive scanning, 60-frame/sec, 1080 Active line standard

- 1250 line, 1:1 Progressive scanning, 50-frame/sec, 1080 Active line standard

In Recommendation ITU-R BT. 709, the Common Image Format (1080 x 1920) is given as preferred format for the new installations, where interoperability with other applications is important. Work is being directed with the aim of reaching a unique world-wide standard.

- c) that a whole range of equipment based on the above systems have been developed or being developed and is commercially available now or soon, including all those necessary for broadcasting chains and for industrial applications;

- ed) that many programs are being produced in both the above systems using the above equipments and that in the development of broadcasting and other services there is an increasing need for HDTV production installations;

- that the use of digital technology and digital interconnection is highly desirable to reach and maintain the level of performance required for HDTV;

- gf) that there are clear advantages for establishing interface specifications for HDTV production installations,

recommends

that the specifications described in this Recommendation should be used as the basic digital coding as well as the bit-parallel and bit-serial interfaces for the 1125/60 and 1250/50 studio signals.

#### ANNEX 1

# 1 Digital representation

# 1.1 Coding characteristics

The signals to be digitized should comply with the characteristics described in Recommendation ITU-R BT.709.

# 1.2 Construction of digital signals

Digital representation of R, G, B, Y,  $C_R$  and  $C_B$  may be obtained using the following relationship. Further study is required in terms of conversion between the data obtained with 8- and 10-bit quantization.

$$R_{d} = \left[ \text{Int} \left\{ (219 \times D) \times E'_{R} + (16 \times D) + 0.5 \right\} \right] / D$$

$$G_{d} = \left[ \text{Int} \left\{ (219 \times D) \times E'_{G} + (16 \times D) + 0.5 \right\} \right] / D$$

$$B_{d} = \left[ \text{Int} \left\{ (219 \times D) \times E'_{B} + (16 \times D) + 0.5 \right\} \right] / D$$

$$Y_{d} = \left[ \text{Int} \left\{ (219 \times D) \times E'_{Y} + (16 \times D) + 0.5 \right\} \right] / D$$

$$C_{Bd} = \left[ \text{Int} \left\{ (224 \times D) \times E'_{CB} + (128 \times D) + 0.5 \right\} \right] / D$$

$$C_{Rd} = \left[ \text{Int} \left\{ (224 \times D) \times E'_{CR} + (128 \times D) + 0.5 \right\} \right] / D$$

where D takes either the value 1 or 4, corresponding to 8-bit or 10-bit quantization respectively; , , and denote analogue R, G, B and luminance signals that have been normalized to span the range 0.0 to 1.0, while and denote analogue colour-difference signals that have been normalized to span the range -0.5 to +0.5.

TABLE 1

Digital coding parameters

| Item | Parameter                                                                                                                       |                           | Value                  |                                    |             |            |                    |                    |

|------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|------------------------------------|-------------|------------|--------------------|--------------------|

|      |                                                                                                                                 | 1125/60 1250/5<br>2:1 1:1 |                        |                                    |             | 0/50       |                    |                    |

|      | Interlace ratio                                                                                                                 | 2:1 1                     |                        |                                    | <u>:1</u>   | <u>2:1</u> | <u>L</u>           |                    |

| 1    | Coded signals $Y$ , $C_B$ , $C_R$ or $R$ , $G$ , $B$                                                                            | 1                         | -                      | obtained fr<br>$E'_Y, E'_R$ –      | •           | •          | •                  | nals,              |

| 2    | Sampling lattice - R, G, B, Y                                                                                                   | Orthogo                   | nal, line a            | nd picture                         | repetitive  |            |                    |                    |

| 3    | Sampling lattice signal - $C_B$ , $C_R$                                                                                         | and with                  | alternate              | nd picture $Y$ samples ed with the | . The first | active co  | lour-diffe         |                    |

| 4    | Number of active lines                                                                                                          | 1035                      |                        |                                    |             |            | 1152               |                    |

| 5    | Sampling frequency <sup>(2)</sup> – R, G, B, Y (MHz)                                                                            |                           | 74.25<br>(74.25/1.001) |                                    |             |            | 72                 | 54                 |

|      | – tolerance                                                                                                                     |                           | =                      | ± 10 x 10-6                        | 6           |            | ± <del>0.1</del> 1 | x 10 <sup>-6</sup> |

| 6    | Sampling frequency <sup>(2)</sup> – <i>CB</i> , <i>CR</i>                                                                       | Half of l                 | uminance               | sampling                           | frequency   | 7          |                    |                    |

| 7    | Number of samples/line                                                                                                          |                           |                        |                                    |             |            |                    |                    |

|      | -R,G,B,Y                                                                                                                        |                           | 2200                   |                                    | <u>23</u>   | <u>76</u>  | 2304               | 1728               |

|      | $-C_B, C_R$                                                                                                                     |                           | 1100                   |                                    | <u>11</u>   | 88         | 1152               | 864                |

| 8    | Number of active samples/line                                                                                                   |                           |                        |                                    |             |            |                    |                    |

|      | -R,G,B,Y                                                                                                                        | 1920                      |                        |                                    |             |            | 1440               |                    |

|      | $-C_B, C_R$                                                                                                                     | 960                       |                        |                                    |             | 720        |                    |                    |

| 9    | Position of the first active $Y$ , $C_B$ , $C_R$ sampling instants with respect to the analogue sync timing reference $O_H$ (6) | 192 <i>T</i>              |                        |                                    | <u>30</u>   | <u>9 T</u> | 256 T              | 192 T              |

|      | respect to the analogue sync                                                                                                    |                           |                        |                                    |             |            |                    |                    |

#### - 4 -11/32 (Rev.1)-E

#### TABLE 1 (CONTINUED)

|   | Item | Parameter                                                                                                                                                                |                                 |           | Value                   |            |                          |  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------|-------------------------|------------|--------------------------|--|

|   |      |                                                                                                                                                                          | 1125/60                         |           |                         | 1250       | 0/50                     |  |

|   |      | Interlace ratio                                                                                                                                                          | 2:1                             | 1:        | :1                      |            | 2:1                      |  |

| - | 10   | Coding format                                                                                                                                                            | Uniformly quantize              | ch of the | video com<br>10 bit/san | -          | gnals  10 bit preferable |  |

|   | 11   | Quantization level assignment <sup>(3)</sup>                                                                                                                             |                                 |           |                         |            |                          |  |

|   |      | <ul><li>Video data</li></ul>                                                                                                                                             |                                 |           | through 25              |            |                          |  |

| Ц |      | Timing reference                                                                                                                                                         | 0.00 <u>thro</u>                | ugh 0.75  | _and 255.0              | 00 through | <u>1 255.75</u>          |  |

|   | 12   | Quantization levels <sup>(4)</sup> - Black level <i>R</i> , <i>G</i> , <i>B</i> , <i>Y</i> - Achromatic level <i>C<sub>B</sub></i> , <i>C<sub>R</sub></i> - Nominal peak |                                 |           | 16.00<br>128.00         |            |                          |  |

|   |      | $- R,G,B,Y$ $- C_B, C_R$                                                                                                                                                 |                                 | 16.0      | 235.00<br>00 and 240    | 0.00       |                          |  |

|   | 13   | Filter characteristics (5)                                                                                                                                               | see Recommendation ITU-R BT.709 |           |                         |            |                          |  |

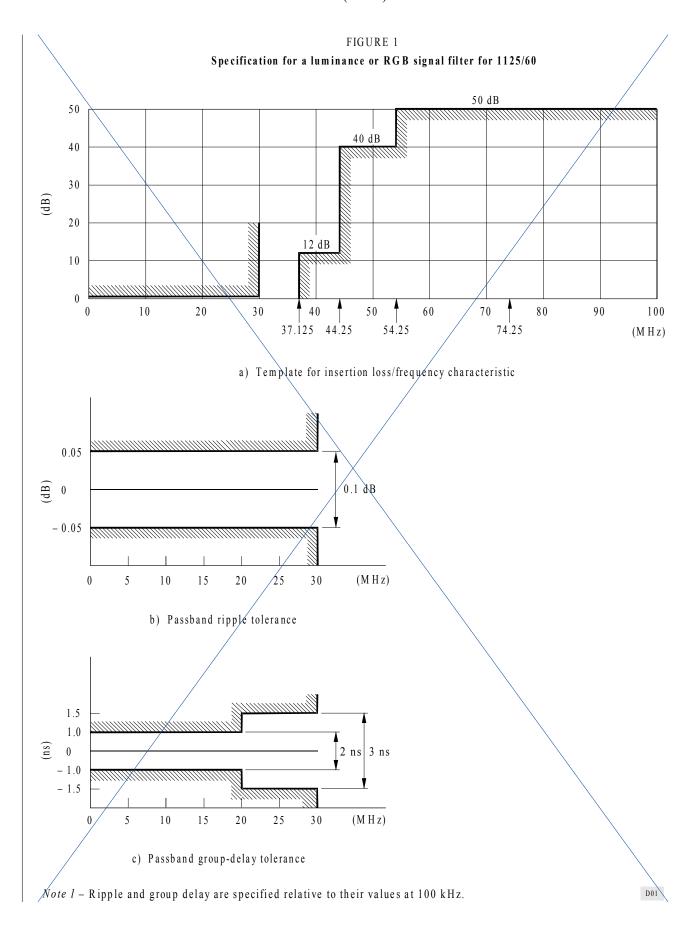

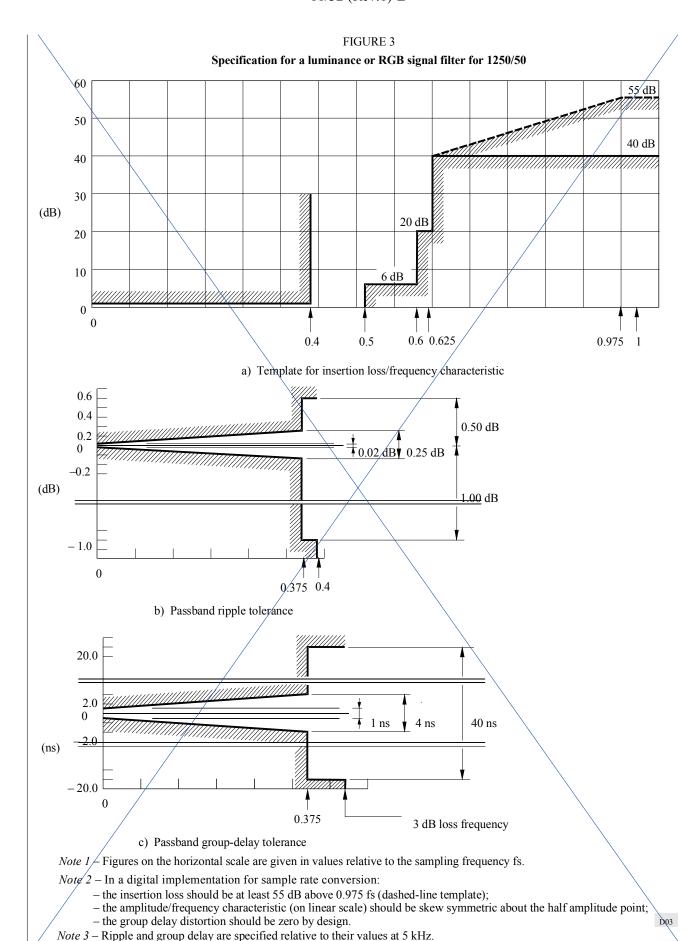

|   |      | R,G,B,Y                                                                                                                                                                  | See Fig. 1                      |           |                         | See F      | <del>lig. 3</del>        |  |

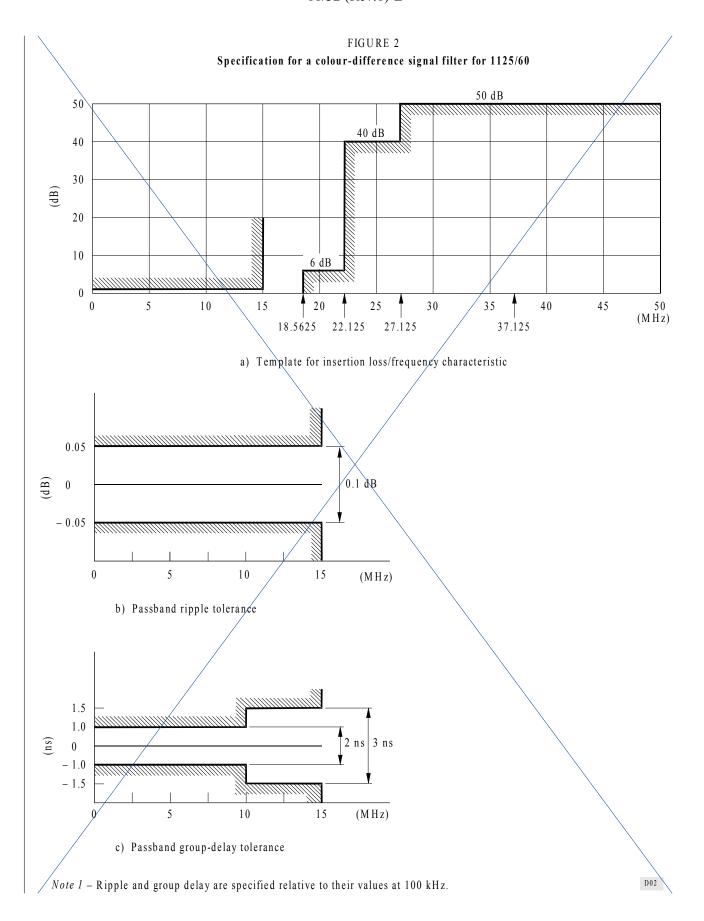

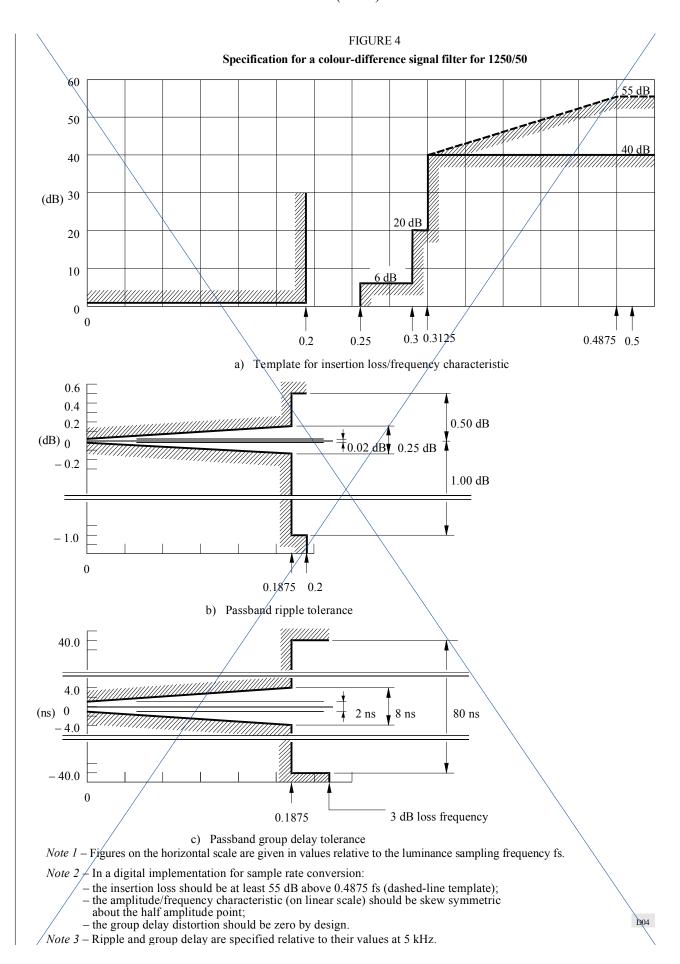

|   |      | $-C_B, C_R$                                                                                                                                                              | See Fig. 2                      |           |                         | See F      | <del>Fig. 4</del>        |  |

- (1) The values for  $E'_R E'_Y$  and  $E'_R E'_Y$  are assumed to be re-normalized.

- (2) The sampling clock must be locked to the line frequency. The values in parentheses are those for the systems having the field/frame frequency of 60/1.001 Hz.-

- (3) To reduce confusion when using 8-bit and 10-bit systems together, the two LSB of the 10-bit system are read as two fractional bits. The quantization scale in an 8-bit system reaches from 0 to 255 in steps of 1, and in a 10-bit system from 0.00 to 255.75 in steps of 0.25.

- (4) These levels refer to precise nominal video levels. Signal processing may occasionally cause the signal level to deviate outside these ranges.

- (5) For 1125/60, the characteristics are specified as a design guideline. For 1250/50, the templates specified facilitate the implementation of practical filters. For 1250/50 with 1440 active samples, the templates specified for 1080/50 systems can be applied because they describe in relative values to the sampling frequency.

- (6) *T* denotes the clock period or the reciprocal of the luminance sampling frequency. For 1125/60, 13.468 ns when the sampling frequency is 74.25 MHz and 13.481 ns when the sampling frequency is (74.25/1.001) MHz. For 1250/50, values are 13.889 ns when the sampling frequency is 72 MHz and 18.519 ns when the sampling frequency is 54 MHz.

- 5 -11/32 (Rev.1)-E

- 6 -11/32 (Rev.1)-E

#### 2 Digital interface

The interface provides a unidirectional interconnection between a single source and a single destination. The data signals are in the form of binary information and are coded accordingly:

- video data (8-bit or 10-bit words for 1125/60 and 1250/50);

- timing reference and identification codes (8-bit or 10-bit words for 1125/60, 10-bit words only for 1250/50 except for 1250/50/2:1/1152 systems, which use 10-bit words only);

- ancillary data (yet to be defined see Recommendation ITU-R BT.1364).

#### 2.1 Video data

Y,  $C_R$ ,  $C_B$  signals are handled as 20-bit words by time-multiplexing  $C_R$  and  $C_B$  components. Each 20-bit word corresponds to a colour-difference sample and a luminance sample. The multiplex is organized as:

$$(C_{B1} Y_1) (C_{R1} Y_2) (C_{B3} Y_3) (C_{R3} Y_4) ...$$

where  $Y_i$  indicates the *i*-th active sample of a line, while  $C_{Bi}$  and  $C_{Ri}$  indicate the colour-difference samples of  $C_R$  and  $C_B$  components co-sited with the  $Y_i$  sample. Note that the index "i" on colour-difference samples takes only odd values due to the half-rate sampling of the colour-difference signals.

The data words corresponding to digital levels 0.00 through 0.75 and 255.00 through 255.75 are reserved for data identification purposes and must not appear as video data.

For 1125/60 and 1250/50/1080, R, G, B signals are handled as 30-bit words in addition to the above 20-bit words for Y,  $C_B$ ,  $C_R$  signals.

# 2.2 Video timing relationship with analogue waveform

For 1125/60, the digital line occupies 2200 clock periods. It begins at 88 clock periods prior to the reference transition (O<sub>H</sub>) of the analogue synchronizing signal in the corresponding line. The digital active line begins at 192 clock periods after the reference transition (O<sub>H</sub>).

For 1250/50 at 72 MHz sampling frequency, the digital line occupies 2304 clock periods. It begins at 128 clock periods prior to the reference transition (O<sub>H</sub>) of the analogue synchronizing signal in the corresponding line. The digital active line begins at 256 clock periods after the reference transition (O<sub>H</sub>).

For 1250/50 at 54 MHz sampling rate, the digital line occupies 1728 clock periods. It begins at 96 clock periods prior to the reference transition (O<sub>H</sub>) of the analogue synchronizing signal in the corresponding line. The digital active line begins at 192 clock periods after the reference transition (O<sub>H</sub>).

The digital line occupies  $\underline{m}$  clock periods. It begins at  $\underline{f}$  clock periods prior to the reference transition (O<sub>H</sub>) of the analogue synchronizing signal in the corresponding line. The digital active line begins at  $\underline{g}$  clock periods after the reference transition (O<sub>H</sub>). The values for  $\underline{m}$ ,  $\underline{f}$  and  $\underline{g}$  are listed in Table 2. See Fig. 51 and Table 2 for detailed timing relationships in the line interval.

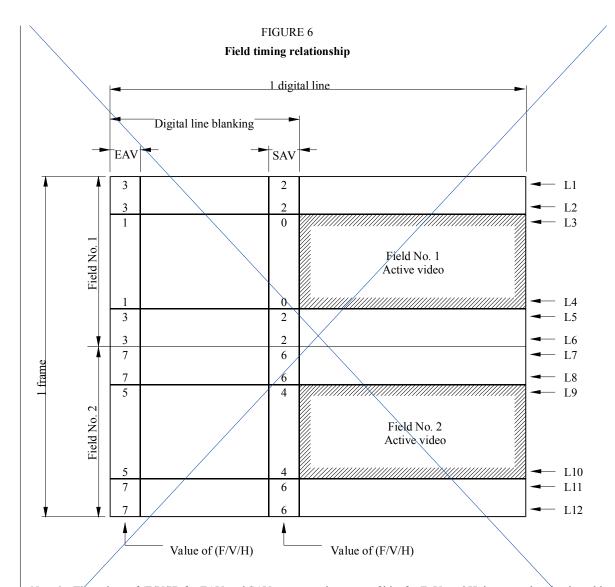

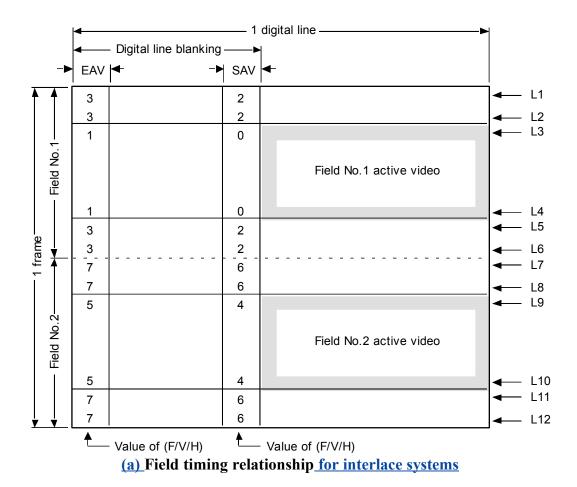

<u>For interlace systems</u>, the start of digital field is fixed by the position specified for the start of the digital line. See Fig. 62(a) and Table 3(a) for detailed relationships in the field interval.

# - 10 -11/32 (Rev.1)-E

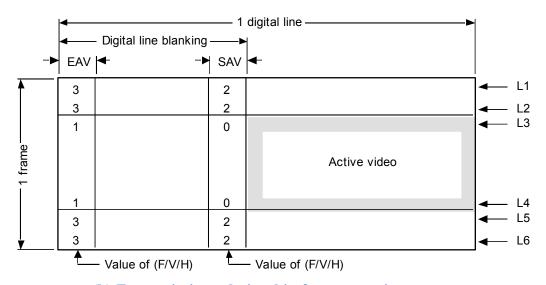

For progressive systems, the start of the digital frame is fixed by the position specified for the start of the digital line. See Fig. 2(b) and Table 3(b) for detailed relationships in the frame interval.

# 2.3 Video timing reference codes (SAV and EAV)

There are two timing reference codes, one at the beginning of each video data block (start of active video; SAV) and the other at the end of each video data block (end of active video; EAV). These codes are contiguous with the video data, and continue during the field/frame blanking interval, as shown in Fig. 62.

Each code consists of a four-word sequence. The bit assignment of the word is given in Table 4. The first three words are fixed preamble and the fourth word carries the information that defines field identification (F), field/frame blanking period (V), and line blanking period (H). In a 1125/60-8 bit implementation bits Nos. 9 to 2 inclusive are used; note in 1250/50 all 10 bits are required.

The bits F and V change state synchronously with EAV at the beginning of the digital line.

Analogue line blanking

(a)

Analogue active line (b)

Analogue full line (c)

(d)

Video data block (h)

E

A

A

V

Video data (Y, R, G, B)

A

V

Multiplexed video data (C

B

C

R

Digital line blanking

Digital line (n)

Dos

$\label{eq:FIGURE} \textbf{5}\underline{\underline{\underline{1}}}$  Data format and timing relationship to analogue waveform

# TABLE 2 Line interval timing specifications

| Symbol | Parameter                                                                  |                             |                             | Va           | lue               |            |               |

|--------|----------------------------------------------------------------------------|-----------------------------|-----------------------------|--------------|-------------------|------------|---------------|

|        |                                                                            | 112                         | 5/60                        |              | 125               | 0/50       |               |

|        | <u>Interlace ratio</u>                                                     | <u>2:1</u>                  | <u>1</u> :                  | <u>:1</u>    |                   | <u>2:1</u> |               |

|        | Number of active Y samples per line                                        |                             |                             | 1920         |                   |            | 1440          |

|        | Sampling frequency (MHz)                                                   | 74.25<br>(74.25 /<br>1.001) | 148.5<br>(148.5 /<br>1.001) | <u>148.5</u> | <u>74.25</u>      | 72         | 54            |

| а      | Analogue line blanking (μs)                                                | 3.771<br>(3.775)            | 1.886<br>(1.887)            | 3.071        | <u>6.141</u>      | 6.         | 00            |

| b      | Analogue active line (μs)                                                  | 25.859<br>(25.884)          | 12.929<br>(12.942)          | 12.929       | 25.859            | 26         | .00           |

| С      | Analogue full line (μs)                                                    | 29.630<br>(29.659)          | 14.815<br>(14.830)          | 16.00        |                   | 32.00      |               |

| d      | Duration between end of analogue active video and start of EAV             |                             | 0 –                         | 6 T          |                   | 24 T       | 18 T          |

| е      | Duration between end of SAV and start of analogue active video             |                             | 0 –                         | 6 T          |                   | 24 T       | 18 <i>T</i>   |

| f      | Duration between start of EAV and analogue timing reference O <sub>H</sub> | 88                          | 3 T                         | 14           | <u>7 T</u>        | 128 T      | 96 T          |

| g      | Duration between analogue timing reference O <sub>H</sub> and end of SAV   | 19                          | 2 T                         | 309          | <u>9 T</u>        | 256 T      | 192 <i>T</i>  |

| h      | Video data block                                                           |                             |                             | 1928 T       |                   |            | 1478 <i>T</i> |

| i      | Duration of EAV                                                            |                             |                             | 4            | T                 |            |               |

| j      | Duration of SAV                                                            |                             |                             | 4            | T                 |            |               |

| k      | Digital line blanking                                                      | 28                          | 0 T                         | 45           | <u>6 <i>T</i></u> | 384 T      | 288 T         |

| l      | Digital active line                                                        |                             |                             | 1920 T       |                   |            | 1440 7        |

| m      | Digital line                                                               | 220                         | 00 T                        | 237          | <u>'6 T</u>       | 2304 T     | 1728 7        |

NOTE 1 – The parameter values for analogue specifications expressed by the symbols a, b and c indicate the nominal values.

NOTE 2 – *T* denotes the clock period or the reciprocal of the luminance sampling frequency. For 1125/60, 13.468 ns when the sampling frequency is 74.25 MHz and 13.481 ns when the sampling frequency is (74.25/1.001) MHz. For 1250/50, values are 13.889 ns when the sampling frequency is 72 MHz and 18.519 ns when the sampling frequency is 54 MHz.

NOTE 3 – The values in parentheses are those for the systems having the field/frame frequency of 60/1.001 Hz.

Note 1 – The values of (F/V/H) for EAV and SAV represent the status of bits for F, V, and H, in a way that the three-bit word composed of F, V, H represents a binary number expressed in decimal notation (F corresponding to MSB and H to LSB). For example, the value 3 represents the bits of F = 0, V = 1 and H = 1.

D06

(b) Frame timing relationship for progressive systems

# FIGURE 62

NOTE 1 – The values of (F/V/H) for EAV and SAV represent the status of bits for F, V and H, in a way that the three-bit word composed of F, V, H represents a binary number expressed in decimal notation (F corresponding to MSB and H to LSB). For example, the value 3 represents the bits of F=0, V=1 and H=1.

TABLE 3

(a) Field interval timing specifications for interlace systems

| Symbol | Definition                                 |                 | Digital lin | e number     |       |

|--------|--------------------------------------------|-----------------|-------------|--------------|-------|

|        |                                            | 112             | 5/60        | 125          | 0/50  |

|        | Number of active lines                     | 1035            | 10          | 80           | 1152  |

| L1     | First line of field No. 1                  |                 | #           | 1            |       |

| L2     | Last line of digital field blanking No. 1  | # 40            | # 20        | <u># 80</u>  | # 44  |

| L3     | First line of field No. 1 active video     | # 41            | # 21        | <u># 81</u>  | # 45  |

| L4     | Last line of field No. 1 active video      | # 557           | # 560       | # 6          | 520   |

| L5     | First line of digital field blanking No. 2 | # 558           | # 561       | # 6          | 521   |

| L6     | Last line of field No. 1                   | # 5             | 563         | # 6          | 525   |

| L7     | First line of field No. 2                  | # 5             | 564         | # (          | 526   |

| L8     | Last line of digital field blanking No. 2  | # 602           | # 583       | <u># 705</u> | # 669 |

| L9     | First line of field No. 2 active video     | # 603           | # 584       | <u># 706</u> | # 670 |

| L10    | Last line of field No. 2 active video      | # 1120          | # 1123      | # 1          | 245   |

| L11    | First line of digital field blanking No. 1 | # 1121 # 1124 # |             |              | 246   |

| L12    | Last line of field No. 2                   | # 1             | 125         | # 1          | 250   |

NOTE 1-Digital field blanking No.1 denotes the field blanking period that is prior to the active video of field No.1, and digital field blanking No.2 denotes that prior to the active video of field No.2.

# (b) Frame interval timing specifications for progressive systems

| Symbol    | <u>Definition</u>                    | Digital lin  | <u>ne number</u> |  |  |

|-----------|--------------------------------------|--------------|------------------|--|--|

|           |                                      | 1125/60      | 1250/50          |  |  |

|           | Number of active lines               | <u>10</u>    | 80               |  |  |

| <u>L1</u> | First line of frame                  | #1           |                  |  |  |

| <u>L2</u> | Last line of digital frame blanking  | <u># 41</u>  | <u># 160</u>     |  |  |

| <u>L3</u> | First line of active video           | # 42         | <u>#161</u>      |  |  |

| <u>L4</u> | Last line of active video            | <u>#1121</u> | <u># 1240</u>    |  |  |

| <u>L5</u> | First line of digital frame blanking | <u>#1122</u> | #1241            |  |  |

| <u>L6</u> | Last line of frame                   | # 1125       | <u>#1250</u>     |  |  |

TABLE 4

Bit assignment for video timing reference codes

| Word           |                                                                                                    |           |           |       | Bit nu   | ımber          |                |                |          |        |

|----------------|----------------------------------------------------------------------------------------------------|-----------|-----------|-------|----------|----------------|----------------|----------------|----------|--------|

|                | 9                                                                                                  | 8         | 7         | 6     | 5        | 4              | 3              | 2              | 1        | 0      |

|                | (MSB)                                                                                              |           |           |       |          |                |                |                |          | (LSB)  |

| First          |                                                                                                    |           |           |       |          |                | 1              | 1              | 1        |        |

| Second         | econd 0 0 0 0 0 0 0                                                                                |           |           |       |          |                |                | 0              | 0        |        |

| Third          | nird 0 0 0 0 0 0 0 0                                                                               |           |           |       |          |                |                | 0              | 0        |        |

| Fourth 1 F V H |                                                                                                    |           |           |       |          | P <sub>2</sub> | P <sub>1</sub> | P <sub>0</sub> | 0        | 0      |

| Interlace sys  | $\frac{\text{Interlace system}}{\text{Interlace system}} \qquad \text{F} = 1 \text{ during field}$ |           |           |       |          | during fi      | eld blank      | king           | H<br>EAV | = 1 in |

|                | = 0 during field No. 1                                                                             |           |           |       |          |                | re             |                | SAV      | = 0 in |

| Progressive    | V = 1                                                                                              | during fi | rame blar | nking | H<br>EAV | = 1 in         |                |                |          |        |

|                |                                                                                                    |           |           |       | =0       | elsewher       | <u>re</u>      |                | SAV      | = 0 in |

NOTE  $1 - P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$  in the fourth word are the protection bits (see Table 5).

The value of protection bits,  $P_0$  to  $P_3$ , depends on the F, V and H as shown in Table 5. The arrangement permits one-bit errors to be corrected and two-bit errors to be detected at the receiver, but only in the 8 most-significant bits, as shown in Table 6.

TABLE 5

Protection bits for SAV and EAV

|               | SAV/     | EAV bit  | status   |                        | Protect                | ion bits               |                        |              |              |

|---------------|----------|----------|----------|------------------------|------------------------|------------------------|------------------------|--------------|--------------|

| Bit 9 (fixed) | 8<br>(F) | 7<br>(V) | 6<br>(H) | 5<br>(P <sub>3</sub> ) | 4<br>(P <sub>2</sub> ) | 3<br>(P <sub>1</sub> ) | 2<br>(P <sub>0</sub> ) | 1<br>(fixed) | 0<br>(fixed) |

| 1             | 0        | 0        | 0        | 0                      | 0                      | 0                      | 0                      | 0            | 0            |

| 1             | 0        | 0        | 1        | 1                      | 1                      | 0                      | 1                      | 0            | 0            |

| 1             | 0        | 1        | 0        | 1                      | 0                      | 1                      | 1                      | 0            | 0            |

| 1             | 0        | 1        | 1        | 0                      | 1                      | 1                      | 0                      | 0            | 0            |

| 1             | 1        | 0        | 0        | 0                      | 1                      | 1                      | 1                      | 0            | 0            |

| 1             | 1        | 0        | 1        | 1                      | 0                      | 1                      | 0                      | 0            | 0            |

| 1             | 1        | 1        | 0        | 1                      | 1                      | 0                      | 0                      | 0            | 0            |

| 1             | 1        | 1        | 1        | 0                      | 0                      | 0                      | 1                      | 0            | 0            |

TABLE 6

Error corrections using protection bits (P<sub>3</sub>-P<sub>0</sub>)

| Received bits 5-2                  |     |     | Receive | d bits 8- | 6 for F, | V and H |     |     |

|------------------------------------|-----|-----|---------|-----------|----------|---------|-----|-----|

| for P <sub>3</sub> -P <sub>0</sub> | 000 | 001 | 010     | 011       | 100      | 101     | 110 | 111 |

| 0000                               | 000 | 000 | 000     | -         | 000      | _       | _   | 111 |

| 0001                               | 000 | _   | _       | 111       | _        | 111     | 111 | 111 |

| 0010                               | 000 | _   | _       | 011       | _        | 101     | _   | _   |

| 0011                               | _   | _   | 010     | _         | 100      | _       | _   | 111 |

|                                    |     |     |         |           |          |         |     |     |

| 0100                               | 000 | -   | _       | 011       | _        | _       | 110 | _   |

| 0101                               | _   | 001 | _       | _         | 100      | _       | _   | 111 |

| 0110                               | _   | 011 | 011     | 011       | 100      | _       | _   | 011 |

| 0111                               | 100 | _   | _       | 011       | 100      | 100     | 100 | _   |

|                                    |     |     |         |           |          |         |     |     |

| 1000                               | 000 | -   | _       | _         | _        | 101     | 110 | -   |

| 1001                               | _   | 001 | 010     | _         | _        | _       | _   | 111 |

| 1010                               | _   | 101 | 010     | _         | 101      | 101     | _   | 101 |

| 1011                               | 010 | _   | 010     | 010       | _        | 101     | 010 | _   |

|                                    |     |     |         |           |          |         |     |     |

| 1100                               | _   | 001 | 110     | _         | 110      | _       | 110 | 110 |

| 1101                               | 001 | 001 | _       | 001       | _        | 001     | 110 | _   |

| 1110                               | _   | _   | _       | 011       | _        | 101     | 110 | _   |

| 1111                               | _   | 001 | 010     | _         | 100      | _       | _   | _   |

*Note I* – The error correction applied provides a DEDSEC (double error detection – single error correction) function. The received bits denoted by "–" in the table, if detected, indicate that an error has occurred but cannot be corrected.

# 2.4 Ancillary data

The ancillary signals should comply with the general rules of Recommendation ITU-R BT.<del>11-2/AD</del> (Doc. 11/12)1364.

#### 2.5 Data words during blanking

The data words occurring during digital blanking intervals that are not used for the SAV, the EAV, the timing reference code ANC, or for ancillary data are filled with words corresponding to the following blanking levels, appropriately placed in the multiplexed data:

16.00 for *Y*, *R*, *G*, *B* signals

128.00 for *C<sub>B</sub>/C<sub>R</sub>* (time-multiplexed colour-difference signal).

# 3 Bit-parallel interface

For the <u>systems of 1125/60-system and 1250/50/1080</u>, the bits of the digital code words which describe the video signal are transmitted in parallel by means of 20 or 30 shielded conductor pairs. The 20 conductor pairs are used for the transmission of the signal set consisting of luminance Y and time-multiplexed colour-difference CB/CR components. The 30 conductor pairs are used for the transmission of R, G, B signals or Y, CB/CR components with an additional data stream (auxiliary channel). An additional shielded conductor pair carries the synchronous clock at 74.25 MHz\_(or 74.25/1.001 MHz) for interlace systems and at 148.5 MHz (or 148.5/1.001 MHz) for progressive systems.

For the 1250/50/1152 system, the bits of digital code words that describe the video signal are transmitted in parallel by means of 20 signal pairs, where each pair carries a stream of bits, 10 pairs for luminance data and 10 pairs for time-multiplexed colour-difference data. The 20 pairs can also carry ancillary data. A 21st pair provides a synchronous clock at 36 MHz (when sampling rate is 72 MHz), or at 27 MHz (when sampling rate is 54 MHz).

Data signals are transmitted in NRZ form in real time (unbuffered).

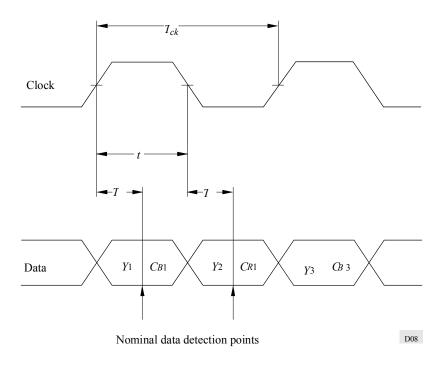

# 3.1 Clock signal and clock-to-data timing relationship

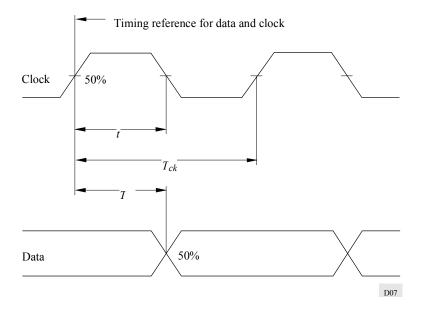

For the systems of 1125/60 and 1250/50/1080, the transmitted clock signal is a 74.25 MHz square wave, of which positive transitions occur midway between the data transitions as shown in Fig. 73 and Table 7.

FIGURE 73 Clock-to-data timing relationship for 1125/60 and 1250/50/1080

For 1250/50/1152 at 72 MHz sampling rate, the transmitted clock signal is a 36 MHz square wave of unity mark/space ratio (27 MHz for 1250/50/1152 at 54 MHz sampling rate), the transitions of which are coincident with the transition of the data (see Fig. 84). A logical high state of the clock is concurrent with Y and  $C_B$  data samples and a logical low state with Y and Y and

TABLE 7

Clock signal specifications

| Parameter                         |                                                                                          | Value 1259/59      |                      |               |                  |                         |

|-----------------------------------|------------------------------------------------------------------------------------------|--------------------|----------------------|---------------|------------------|-------------------------|

|                                   |                                                                                          |                    |                      | 250/50        |                  |                         |

| Interlace ratio                   | 2:1                                                                                      | <u>1:</u>          | 1                    |               | <u>2:1</u>       |                         |

| Sampling frequency for <i>Y</i> , | 74.25                                                                                    | <u>148.5</u>       | <u>148.5</u>         | <u>74.25</u>  | 72               | 54                      |

| R, G, B signals (MHz)             | (74.25 /<br>1.001)                                                                       | (148.5 /<br>1.001) |                      |               |                  |                         |

| Clock period Tck-(ns)             | 1/(220                                                                                   | $00f_H$ )          | 1/(237               | $76f_H$ )     | $1/(1152 f_H)$   | 1/(864 f <sub>H</sub> ) |

| nominal value (ns)                | 13.468                                                                                   | <u>6.734</u>       | <u>6.734</u>         | <u>13.468</u> | 27.778           | 37.038                  |

|                                   | (13.481)                                                                                 | (6.741)            |                      |               |                  |                         |

| Clock pulse width $t$ -(ns)       |                                                                                          |                    | 0.5                  | 5 Tck         |                  |                         |

| tolerance                         |                                                                                          | $\pm 0.11$         | <u>Tck</u>           |               | (nom             | inal)                   |

| Clock jitter                      |                                                                                          | Within ±           | 0.04 <i>Tck</i>      |               | Within ±         | = 0.5 ns                |

|                                   | from the average time of transition over one field over one frame in progressive systems |                    |                      |               | in interlace sys | stems, and              |

| Data timing <i>Td</i> (ns)        |                                                                                          | 0.5 7              | <u>rck</u>           |               | 0.25             | <u>Tck</u>              |

| tolerance                         |                                                                                          | $\pm 0.073$        | <u> 5 <i>Tck</i></u> |               | (nom             | inal)                   |

NOTE  $1 - f_H$  denotes the line frequency.

NOTE 2 – Values are specified at the sending end (source).

NOTE 3 – The values in parentheses are those for the systems having the field/frame frequency of 60/1.001 Hz.

FIGURE <u>84</u>

Clock-to-data timing relationship for 1250/50/1152

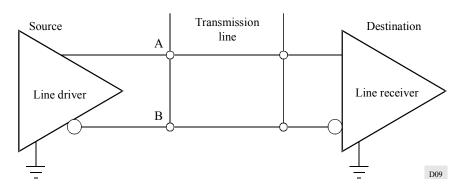

#### 3.2 Electrical characteristics of the interface

The interface employs 21 line drivers and line receivers, in the case of the transmission of Y and  $C_B/C_R$  components. Each line driver has a balanced output and the corresponding line receive has a balanced input. For 1125/60 and 1250/50/1080, the interface employs 31 line drivers and line receivers, in the case of R, G and B components or  $Y C_B/C_R$  with an additional data stream (auxiliary channel).

Although the use of ECL technology is not mandatory, the line driver and receiver must be ECL 10 kHz compatible for 1125/60/2:1 and 1250/50/2:1/1080, and ECL100k compatible for 1250/50/2:1/1152, i.e., they must permit the use of ECL for either drivers or receivers.

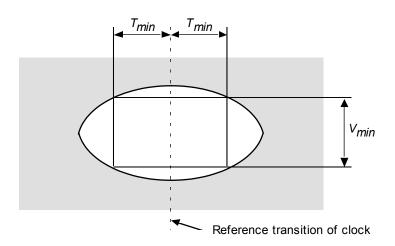

The receiver must sense correctly the data when a random signal produces conditions represented by the eye diagram of Fig. 106.

TABLE 8

Line driver characteristics

| Item | Parameter                                   |                                         | Value                       |         |        |                |              |  |

|------|---------------------------------------------|-----------------------------------------|-----------------------------|---------|--------|----------------|--------------|--|

|      |                                             | 112:                                    | 5/60                        |         | 1250/5 | 0              |              |  |

|      | Sampling frequency (MHz)                    | 74.25<br>(74.25 /<br>1.001)             | 148.5<br>(148.5 /<br>1.001) | 148.5   | 74.25  | <u>72</u>      | <u>54</u>    |  |

| 1    | Output impedance $(\Omega)$                 |                                         | 110 max.                    |         |        |                | 100 max.     |  |

| 2    | Common mode voltage (1) (V)                 |                                         | -1.29                       | ± 15%   |        | -1.3 =         | ± 15%        |  |

| 3    | Signal amplitude <sup>(2)</sup> (V)         |                                         | 0.6 to                      | 2.0 p-p |        | 0.8 to 2.0 p-p |              |  |

| 4    | Rise and fall times (3)-(ns)                | ≤ <del>2.0</del> <u>0.15 <i>Tck</i></u> |                             |         |        | < 3 <u>ns</u>  |              |  |

| 5    | Difference between rise and fall times (ns) |                                         | $\leq 1.0 \ 0.075 \ Tck$    |         |        |                | .0 <u>ns</u> |  |

NOTE 1 - Tck denotes the clock period (see Table 7).

NOTE 2 – The values in parentheses are those for the systems having the field/frame frequency of 60/1.001 Hz.

- (1) Measured relative to ground.

- (2) Measured across a resistive load having the nominal impedance of the assumed cables, that is  $110 \Omega$  for 1125/60 and 1250/50/1080, and  $100 \Omega$  for 1250/50/1152.

- (3) Measured between the 20% and 80% points across a resistive load having the nominal impedance of the assumed cable.

TABLE 9

Line receiver characteristics

| Item | Parameter                               |                             | Value                       |         |        |           |           |

|------|-----------------------------------------|-----------------------------|-----------------------------|---------|--------|-----------|-----------|

|      |                                         | 112:                        | 5/60                        |         | 1250/5 | 0         |           |

|      | Sampling frequency (MHz)                | 74.25<br>(74.25 /<br>1.001) | 148.5<br>(148.5 /<br>1.001) | 148.5   | 74.25  | <u>74</u> | <u>54</u> |

| 1    | Input impedance $(\Omega)$              |                             | $110 \pm 10$                |         |        |           |           |

| 2    | Maximum input signal voltage (V)        |                             | 2.0 p-p                     |         |        |           |           |

| 3    | Minimum input signal voltage (mV)       |                             |                             | 185 p-p | )      |           |           |

| 4    | Maximum common mode voltage (1) (V)     |                             | ± 0.3                       |         |        |           | 0.5       |

| 5    | Differential delay <u>Tmin</u> (2) (ns) |                             | 4.0 <u>0.3 Tck</u>          |         |        |           |           |

NOTE 1 - Tck denotes the clock period (see Table 7).

NOTE 2 – The values in parentheses are those for the systems having the field/frame frequency of 60/1.001~Hz.

- (1) Comprising interference in the range DC to line frequency (fH).

- (2) Data must be correctly sensed when the differential delay between the received clock and data is within this range (see Fig. 6).

FIGURE - 95 Line driver and line receiver interconnection

*T<sub>min</sub>* : 4.0ns for 1125/60 : 4.5 ns for 1250/50 *V<sub>min</sub>* : 100 mV

NOTE 1 – For 1125/60 and 1250/50/1080, the width of the window in the eye diagram, within which data must be correctly detected, comprises  $\pm 0.5$  ns  $\pm 0.04$  T clock jitter,  $\pm 1.0$  ns  $\pm 0.075$  T data timing, and  $\pm 2.5$  ns  $\pm 0.18$  T propagation skew of conductor pairs.

For 1250/50/1152, the aggregate of clock jitter, data timing and propagation skew of conductor pairs must not exceed 4.5 ns.

#### FIGURE 106

Idealized eye diagram corresponding to the minimum input signal level

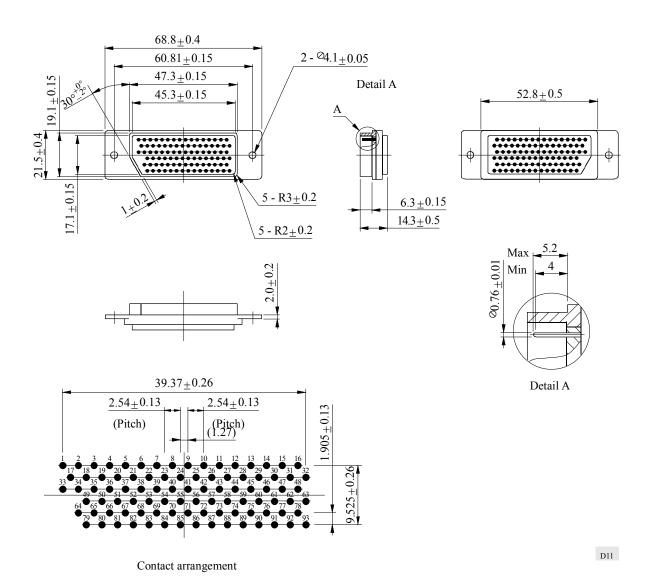

#### 3.3 Mechanical characteristics

#### 3.3.1 Connector

The interface uses a multi-contact connector. Connectors are locked by two screws on the cable connectors and two threaded bolts on the equipment. Cable connectors employ pin contacts and equipment connectors employ socket contacts. Shielding of the connectors and cables is mandatory.

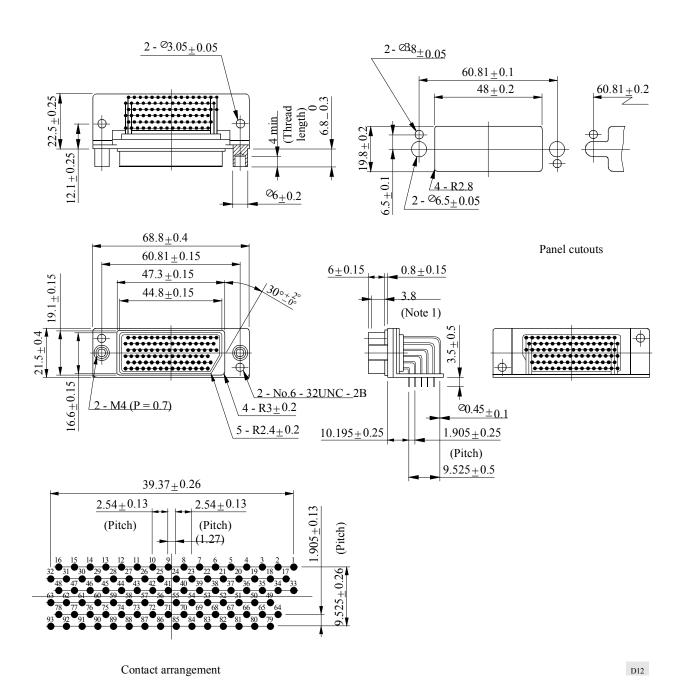

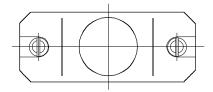

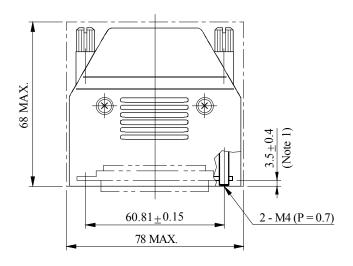

For 1125/60 and 1250/50/1080, a 93-contact connector is used. Contact assignments are indicated in Tables 10 and 11. The mechanical specifications for the connectors are shown in Figs. 417, 428 and 439.

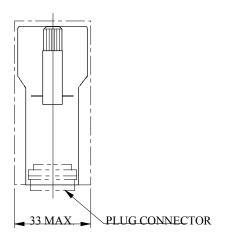

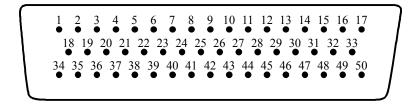

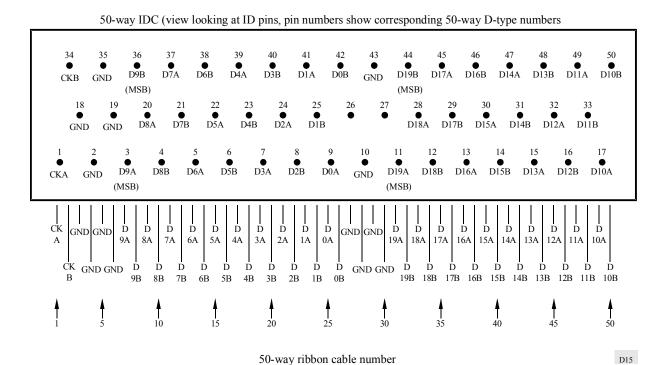

For 1250/50/1152, a 50-contact type D subminiature connector is used. Contact assignments are indicated in Table 12 and Fig. 1410 (for information, suggested contact assignment for a PCB header are shown in Fig. 1511).

TABLE 10 Connector contact assignment for 1125/60 systemand 1250/50/1080

| Con- | Signal  | Con- | Signal | Con- | Signal  | Con- | Signal | Con- | Signal | Con- | Signal |

|------|---------|------|--------|------|---------|------|--------|------|--------|------|--------|

| tact | line    | tact | line   | tact | line    | tact | line   | tact | line   | tact | line   |

| 1    | Clock A | 17   | GND    | 33   | Clock B |      |        |      |        |      |        |

| 2    | XD 9A   | 18   | GND    | 34   | XD 9B   | 49   | YD 4A  | 64   | GND    | 79   | YD 4B  |

| 3    | XD 8A   | 19   | GND    | 35   | XD 8B   | 50   | YD 3A  | 65   | GND    | 80   | YD 3B  |

| 4    | XD 7A   | 20   | GND    | 36   | XD 7B   | 51   | YD 2A  | 66   | GND    | 81   | YD 2B  |

| 5    | XD 6A   | 21   | GND    | 37   | XD 6B   | 52   | YD 1A  | 67   | GND    | 82   | YD 1B  |

| 6    | XD 5A   | 22   | GND    | 38   | XD 5B   | 53   | YD 0A  | 68   | GND    | 83   | YD 0B  |

| 7    | XD 4A   | 23   | GND    | 39   | XD 4B   | 54   | ZD 9A  | 69   | GND    | 84   | ZD 9B  |

| 8    | XD 3A   | 24   | GND    | 40   | XD 3B   | 55   | ZD 8A  | 70   | GND    | 85   | ZD 8B  |

| 9    | XD 2A   | 25   | GND    | 41   | XD 2B   | 56   | ZD 7A  | 71   | GND    | 86   | ZD 7B  |

| 10   | XD 1A   | 26   | GND    | 42   | XD 1B   | 57   | ZD 6A  | 72   | GND    | 87   | ZD 6B  |

| 11   | XD 0A   | 27   | GND    | 43   | XD 0B   | 58   | ZD 5A  | 73   | GND    | 88   | ZD 5B  |

| 12   | YD 9A   | 28   | GND    | 44   | YD 9B   | 59   | ZD 4A  | 74   | GND    | 89   | ZD 4B  |

| 13   | YD 8A   | 29   | GND    | 45   | YD 8B   | 60   | ZD 3A  | 75   | GND    | 90   | ZD 3B  |

| 14   | YD 7A   | 30   | GND    | 46   | YD 7B   | 61   | ZD 2A  | 76   | GND    | 91   | ZD 2B  |

| 15   | YD 6A   | 31   | GND    | 47   | YD 6B   | 62   | ZD 1A  | 77   | GND    | 92   | ZD 1B  |

| 16   | YD 5A   | 32   | GND    | 48   | YD 5B   | 63   | ZD 0A  | 78   | GND    | 93   | ZD 0B  |

Note 1 - XD 9-XD 0, YD 9-YD 0, and ZD 9-ZD 0 represent each bit of the component signals. The suffix 9 to 0 indicates the bit number (bit 9 denotes MSB). A and B correspond to the terminals A and B of Fig. 95, respectively. The relationship between XD, YD, ZD and component signals are specified in Table 10.

*Note 2* – The shield of each pair uses the ground contact (GND) located between A and B contacts for the signal, e.g., contact No. 17 is used for the shield of the clock signal. The overall shield of the cable is electrically connected to connector hood, which is grounded to the frame of the equipment.

TABLE 11

93-pin multi-pin connector (plug) for 1125/60 and 1250/50/1080

| Transmission              | Component         | Component Signal line assignment |              | Cable    |

|---------------------------|-------------------|----------------------------------|--------------|----------|

| signal set                |                   | 10 bit system                    | 8-bit system |          |

| $Y, C_R/C_B$              | Y                 | XD 9-XD 0                        | XD 9-XD 2    |          |

|                           | $C_R/C_B$         | ZD 9-ZD 0                        | ZD 9-ZD 2    | 21 pairs |

| $Y, C_R/C_B$              | Y                 | XD 9-XD 0                        | XD 9-XD 2    |          |

| with auxiliary<br>channel | $C_R/C_B$         | ZD 9-ZD 0                        | ZD 9-ZD 2    |          |

|                           | Auxiliary channel | YD 9-YD 0                        | YD 9-YD 2    | 31 pairs |

|                           | G                 | XD 9-XD 0                        | XD 9-XD 2    |          |

| R, G, B                   | В                 | YD 9-YD 0                        | YD 9-YD 2    |          |

|                           | R                 | ZD 9-ZD 0                        | ZD 9-ZD 2    |          |

# 3.3.2 Interconnecting cable

For 1125/60 and 1250/50/1080, two types of multi-channel cable, either 21 or 31 channels, can be used in accordance with the transmission signal set (see Table 11). The cable consists of twisted pairs with <u>an</u> individual shield <u>offor</u> each pair. It also contains an overall shield. The nominal characteristic impedance of each twisted pair is  $110 \Omega$ . The cable shall <u>providepossess</u> the characteristics that satisfy the conditions of <u>the</u> eye diagram shown in Fig. <u>106</u> up to a maximum cable length of 20 m for the interlace systems and 14 m for the progressive systems, respectively.

For 1250/50/1152, 21-channel balanced conductor pairs is used. The nominal characteristic impedance of each conductor pair is  $100 \Omega$ . Cable length up to 30 m may be employed when a high-quality cable is used.

# FIGURE <u>4+7</u> 93-pin multi-pin connector (plug) for 1125/60 and 1250/50/1080

FIGURE <u>128</u>

93-pin multi-pin connector (receptacle) for 1125/60 and 1250/50/1080

# FIGURE 139

# 93-pin multi-pin connector (hood) for 1125/60 and 1250/50/1080

Note 1 – A screw projecting out from the plug connector.

Note 2 – Applicable outer diameter:

17.5 min to 19.3 max and 21.1 min to 23.2 max.

D13

TABLE 12

Connector contact assignment for 1250/50/1152

| Contact | Signal<br>line | Contact | Signal<br>line | Contact | Signal<br>line |

|---------|----------------|---------|----------------|---------|----------------|

| 1       | Clock A        |         |                | 34      | Clock B        |

| 2       | GND            | 18      | GND            | 35      | GND            |

| 3       | Data 9A        | 19      | GND            | 36      | Data 9B        |

| 4       | Data 8B        | 20      | Data 8A        | 37      | Data 7A        |

| 5       | Data 6A        | 21      | Data 7B        | 38      | Data 6B        |

| 6       | Data 5B        | 22      | Data 5A        | 39      | Data 4A        |

| 7       | Data 3A        | 23      | Data 4B        | 40      | Data 3B        |

| 8       | Data 2B        | 24      | Data 2A        | 41      | Data 1A        |

| 9       | Data 0A        | 25      | Data 1B        | 42      | Data 0B        |

| 10      | GND            | 26      | GND            | 43      | GND            |

| 11      | Data 19A       | 27      | GND            | 44      | Data 19B       |

| 12      | Data 18B       | 28      | Data 18A       | 45      | Data 17A       |

| 13      | Data 16A       | 29      | Data 17B       | 46      | Data 16B       |

| 14      | Data 15B       | 30      | Data 15A       | 47      | Data 14A       |

| 15      | Data 13A       | 31      | Data 14B       | 48      | Data 13B       |

| 16      | Data 12B       | 32      | Data 12A       | 49      | Data 11A       |

| 17      | Data 10A       | 33      | Data 11B       | 50      | Data 10B       |

*Note I* – Data 9-Data 0 represent each bit of the luminance signal (Y), and Data 19-Data 10 that of time-multiplexed colour-difference signal ( $C_R/C_B$ ). The suffix 19 to 0 indicates the bit number (bit 19 denotes MSB for  $C_R/C_B$  and bit 9 MSB for Y). A and B correspond to the terminals A and B of Fig. 95, respectively.

# FIGURE 1410

Mating face of connector receptacle containing male pins (plug) for 1250/50/1152

Note 1 – The preferred orientation for connectors, mounted vertically or horizontally, is with contact 1 uppermost.

D14

#### FIGURE 1511

# Suggested contact assignment for PCB header for 1250/50/1152

#### 4 Bit-serial interface

Specifications for progressive systems are under study.

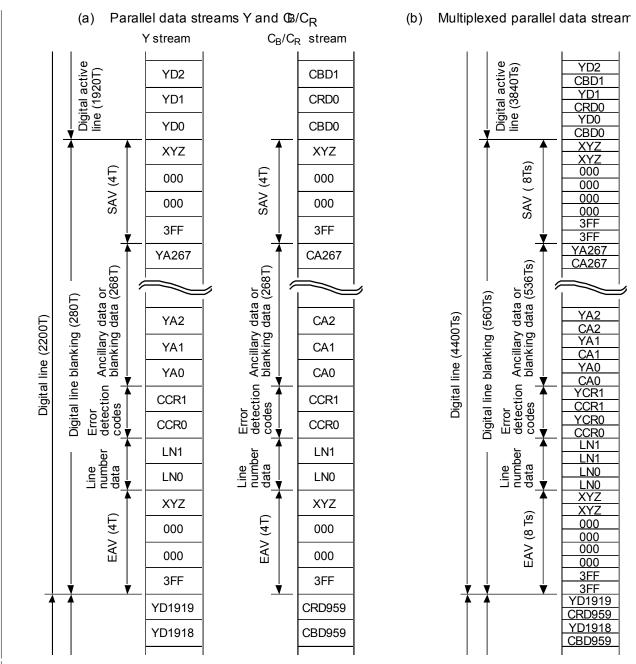

#### 4.1 Data format

The bit-serial data consists of video data, video timing reference codes, line number data, error detection codes, ancillary data and blanking data. Each data has a word-length of 10 bits, and is represented as parallel data before serialization. Two parallel streams (i.e. luminance data Y and colour-difference data  $C_B/C_R$ ) are multiplexed and serialized in accordance with § 4.2.

#### 4.1.1 Video data

The video data should be 10-bit words representing Y,  $C_B/C_R$  of the video systems defined in § 1.

#### 4.1.2 Video timing reference codes

The video timing reference codes, SAV and EAV have the same format as that defined in § 2.

#### 4.1.3 Line number data

The line number data is composed of two words indicating the line number. The bit assignment of the line number data is shown in Table 13. The line number data should be located immediately after EAV.

TABLE 13

Bit assignment of the line number data

| Word | b9<br>(MSB) | b8 | b7 | b6 | b5  | b4 | b3 | b2 | b1 | b0<br>(LSB) |

|------|-------------|----|----|----|-----|----|----|----|----|-------------|

| LN0  | not b8      | L6 | L5 | L4 | L3  | L2 | L1 | L0 | R  | R           |

| LN1  | not b8      | R  | R  | R  | L10 | L9 | L8 | L7 | R  | R           |

L0 (LSB)-L10 (MSB): line number in binary code

R: reserved (set to zero)

#### 4.1.4 Error detection codes

The error detection codes CRCC (cyclic redundancy check codes), which are used to detect errors in active digital line, EAV and line number data, consist of two words and are determined by the following polynomial generator equation:

$$EDC(x) = x^{18} + x^5 + x^4 + 1$$

Initial value of the codes is set to zero. The calculation starts at the first word of the digital active line and ends at the final word of the line number data. Two error detection codes are calculated, one for luminance data, *YCR*, and one for colour-difference data, *CCR*. The bit assignment of the error detection codes is shown in Table 14. The error detection codes should be located immediately after the line number data.

TABLE 14

Bit assignment for error detection codes

| Word | b9<br>(MSB) | b8    | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0<br>(LSB) |

|------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|

| YCR0 | not b8      | CRC8  | CRC7  | CRC6  | CRC5  | CRC4  | CRC3  | CRC2  | CRC1  | CRC0        |

| YCR1 | not b8      | CRC17 | CRC16 | CRC15 | CRC14 | CRC13 | CRC12 | CRC11 | CRC10 | CRC9        |

| CCR0 | not b8      | CRC8  | CRC7  | CRC6  | CRC5  | CRC4  | CRC3  | CRC2  | CRC1  | CRC0        |

| CCR1 | not b8      | CRC17 | CRC16 | CRC15 | CRC14 | CRC13 | CRC12 | CRC11 | CRC10 | CRC9        |

NOTE 1 – CRC0 is the MSB of error detection codes

#### 4.1.5 Ancillary data

The ancillary data should comply with general rules of Recommendation [ITU-R BT., Doc.11/12(Rev.1)]ITU-R BT. 1364.

#### 4.1.6 Blanking data

The blanking data words during digital blanking intervals that are not used for SAV, EAV, the line number data, the error detection codes and the ancillary data, should be filled with the words corresponding to the following quantization levels:

16.00 for *Y* data

# - 31 -11/32 (Rev.1)-E

128.00 for  $C_B/C_R$  data

#### 4.2 Transmission format

The two parallel data streams are transmitted over a single channel in bit-serial form after word-multiplexing, parallel-to-serial conversion and scrambling.

# 4.2.1 Word-multiplexing

The two parallel streams should be multiplexed word by word into a single 10-bit parallel stream in the order of  $C_B$ , Y,  $C_R$ , Y,  $C_R$ , Y,  $C_R$ , Y, .........(See Fig. 1612)

#### 4.2.2 Serializing

The least significant bit (LSB) of each 10-bit word in the word-multiplexed parallel stream should be transmitted first in the bit-serial format.

### 4.2.3 Channel coding

The channel coding scheme should be scrambled NRZI (non-return to zero inverted). The serialized bit stream should be scrambled using the following generator polynomial equation:

$$G(x) = (x^9 + x^4 + 1)(x+1)$$

The input signal to the scrambler shall be positive logic. (The high voltage represents data 1 and the lowest voltage represents data 0.)

#### 4.2.4 Bit-serial digital check field

Digital test signals suitable for testing cable equalization and phase locked loop (PLL) lock-in are described in Appendix.

The LSB of each word should be transmitted first when it is transmitted as bit-serial data.

| YD0 Ð YD1919  | Digital luminance data Y                                    |

|---------------|-------------------------------------------------------------|

| CBD0 Đ CBD959 | Digital colour-difference data $C_B$                        |

| CRD0 Ð CRD959 | Digital colour-difference data $C_R$                        |

| YA0 Đ YA267   | Ancillary data or blanking data in Y stream                 |

| CA0 Đ CA267   | Ancillary data or blanking data in $C_B/C_R$ stream         |

| T             | 1/74.25  MHz = 13.468  ns or  1.001/74.25  MHz = 13.481  ns |

| $T_S = T/2$   |                                                             |

FIGURE 1612

Data stream for 1125/60/2:1 signal

#### 4.3 Coaxial cable interfaces

The coaxial cable interfaces consists of one source and one destination in a point-to-point connection. The coaxial cable interfaces specify the characteristics of line driver (source), line receiver (destination), transmission line and connectors.

#### 4.3.1 Line driver characteristics (source)

Table 15 specifies the line driver characteristics. The line driver should have an unbalanced output circuit.

TABLE 15

Line driver characteristics

| Item | Parameter                             | Value                                                                                                                                        |

|------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Output impedance                      | 75 Ω nominal                                                                                                                                 |

| 2    | DC offset (1)                         | $0.0 \text{ V} \pm 0.5 \text{ V}$                                                                                                            |

| 3    | Signal amplitude (2)                  | 800 mV <sub>p-p</sub> ± 10%                                                                                                                  |

| 4    | Return loss                           | $\geq 15 \text{ dB (3)}, \geq 10 \text{ dB (4)}$                                                                                             |

| 5    | Rise and fall times (5)               | <270 ps (20% to 80%)                                                                                                                         |

| 6    | Difference between rise and fall time | ≤ 100 ps                                                                                                                                     |

| 7    | Output jitter (6)                     | $f_1 = 10 \text{ Hz}$<br>$f_3 = 100 \text{ kHz}$<br>$f_4 = 1/10 \text{ of the clock rate}$<br>A1 = 1  UI (UI; unit interval)<br>A2 = 0.2  UI |

- (1) Defined by mid-amplitude point of the signal.

- (2) Measured across a  $75\Omega$  resistive load connected through a 1 meter coaxial cable.

- (3) In the frequency range of 5 MHz to 742.5 MHz.

- (4) In the frequency range of 742.5 MHz to 1.485 GHz.

- (5) Determined between the 20% and 80% amplitude points and measured across a 75  $\Omega$  resistive load. Overshoot of the rising and falling edges of the waveform shall not exceed 10% of the amplitude.

- (6) For 1125/60 system, 1 UI and 0.2 UI correspond to 673 ps and 135 ps, respectively. For 1250/50 system, 1 UI and 0.2 UI correspond to 694 ps (72 MHz sampling), 926 ps (54 MHz sampling) and 139 ps (72 MHz sampling), 185 ps (54 MHz sampling), respectively. Specification of jitter and jitter measurements methods shall comply with Recommendation ITU-R BT.[Doc. 11/83] (Jitter specifications and jitter measurement methods of bit-serial signals conforming to Recommendation ITU-R BT.656, ITU-R BT.799 and ITU-R BT.1120).

Output amplitude excursions due to signals with a significant dc component occurring for a horizontal line (pathological signals) shall not exceed 50 mV above or below the average peak-peak signal envelope. (In effect, this specification defines a minimum output coupling time constant.)

#### 4.3.2 Line receiver characteristics (destination)

Table 16 specifies the line receiver characteristics. The line receiver should have an unbalanced input circuit. It must sense correctly the received data when connected to a line driver operating at the extreme voltage limits permitted by § 4.3.1, and when connected through a cable having the worst condition permitted by § 4.3.3.

TABLE 16

Line receiver characteristics

| Item | Parameter          | Value                                            |                 |  |

|------|--------------------|--------------------------------------------------|-----------------|--|

| 1    | Input impedance    | 75 Ω nominal                                     |                 |  |

| 2    | Return loss        | $\geq 15 \text{ dB (1)}, \geq 10 \text{ dB (2)}$ |                 |  |

|      |                    | $\pm 2.5 \text{ V}_{\text{max}}$                 | DC              |  |

| 3    | Interfering signal | < 2.5 V <sub>p-p</sub>                           | below 5 kHz     |  |

|      |                    | < 100 mV <sub>p-p</sub>                          | 5 kHz to 27 MHz |  |

|      |                    | < 40 mV <sub>p-p</sub>                           | above 27 MHz    |  |

| 4    | Input jitter (3)   | to be defined                                    |                 |  |

- (1) In the frequency range of 5 MHz to 742.5 MHz.

- (2) In the frequency range of 742.5 MHz to 1.485 GHz.

- (3) Specification of jitter and jitter measurements methods shall comply with Recommendation ITU-R BT. [Doc. 11/83] (Jitter specifications and jitter measurement methods of bit-serial signals conforming to Recommendations ITU-R BT.656, ITU-R BT.799 and ITU-R BT.1120).

Values for input jitter need to be defined. Input jitter is measured with a short cable (2 m).

#### 4.3.3 Transmission line characteristics

Relevant specifications are given in Table 17.

TABLE 17

Transmission line characteristics

| Item | Parameter             | Value                          |  |

|------|-----------------------|--------------------------------|--|

| 1    | Transmission loss (1) | ≤ 20 dB at 1/2 clock frequency |  |

| 2    | Return loss           | ≥15 dB (2), ≥10 dB (3)         |  |

| 3    | Impedance             | 75 Ω nominal                   |  |

- (1) Loss characteristics of  $1/\sqrt{f}$ .

- (2) In the frequency range of 5 MHz to 742.5 MHz.

- (3) In the frequency range of 742.5 MHz to 1.485 GHz.

#### 4.3.4 Connector

The connector should have the mechanical characteristics conforming to the standard BNC type defined in IEC 169-8, and its electronic characteristics should provide for a characteristic impedance of 75  $\Omega$  and for a usable frequency range of up to 2.4 GHz.

# 4.4 Optical fibre interfaces

Optical interfaces should use single mode optical interfaces only and should comply with general rules of ITU-R Recommendation BT.[Doc. 11/78(Rev.1)] (Serial Digital Fiber Transmission Systems for Signals Conforming to Recommendations ITU-R BT.656, ITU-R BT.799 and ITU-R BT.1120).

To make use of this Recommendation the following specifications are necessary:

Rise and fall times < 270 ps (20% to 80%)

output jitter (See Note 1)  $f_1 = 10 \text{ Hz}$

$f_3 = 100 \text{ kHz}$

$f_4 = 1/10$  of the clock rate

A1 = 0.135 UI (UI; unit interval)

A2 = 0.135 UI

Input jitter needs to be defined. Input jitter is measured with a short cable (2 m).

NOTE 1 - Specification of jitter and jitter measurements methods shall comply with Recommendation ITU-R BT.[Doc. 11/83] (Jitter specifications and jitter measurement methods of bit-serial signals conforming to Recommendations ITU-R BT. ITU-R BT.656, 799 and ITU-R BT.1120).

#### **APPENDIX TO ANNEX 1**

# **Bit-Serial Digital Checkfield for Use in HDTV Digital Interfaces**

#### 1 Scope

This Appendix specifies digital test signals suitable for evaluating the low-frequency response of equipment handling HDTV serial digital video signals. Although a range of signals will produce the desired low-frequency effects, two specific signals are defined to test cable equalization and phase locked loop (PLL) lock-in, respectively. In the past, these two signals have been colloquially called "pathological signals."

#### **2** General considerations

Stressing of the automatic equalizer is accomplished by using a signal with the maximum number of ones or zeros, with infrequent single clock period pulses to the opposite level. Stressing of the phase locked loop is accomplished by using a signal with a maximum low-frequency content; that is, with a maximum time between level transitions.

2.1 Channel coding of the serial digital signal defined by Recommendation ITU-R BT.1120 utilizes scrambling and encoding into NRZI (non return to zero, inverted) accomplished by a concatenation of the two following functions:

$$G_1(X) = X^9 + X^4 + 1$$

$G_2(X) = X + 1$

As a result of the channel coding, long runs of zeros in the G2 (X) output data can be obtained when the scrambler, G1 (X), is in a certain state at the time when the specific words arrive. That certain state will be present on a regular basis; therefore, continuous application of the specific data words will regularly produce the low-frequency effects.

- 2.2 Although the longest run of parallel data zeros (40 consecutive zeros) will occur during the EAV/SAV TRS words, the frequency with which the scrambling of the TRS words coincide with the required scrambler state to permit either stressing condition is low. In the instances where this coincident occurs, the generation of the stressing condition is so time limited that equalizers and phase locked loops are not maximally stressed.

- 2.3 In the data portions of digital video signals (excluding TRS words in EAVs or SAVs, and ANC data flag words), the sample values are restricted to exclude data levels 0 to 3 and 1020 to 1023 (000h to 003h and 3FCh to 3FFh in 10-bit hexadecimal representation and 00.0 to 00.C and FF.0 to FF.C, in 8.2 hexadecimal notation). The result of this restriction is that the longest run of zeros, at the scrambler input, is 16 (bits), occurring when a sample value of 200h is followed by a value between 004h and 007h. This situation can produce up to 26 consecutive zeros at the NRZI output, which is (also) not a maximally stressed case.

- 2.4 Other specific data words in combination with specific scrambler states can produce a repetitive low-frequency serial output signal until the next EAV or SAV affects the scrambler state. It is these combinations of data words that form the basis of the test signals defined by this practice.

- 2.5 Because of the Y/C interleaved nature of the component digital signal, it is possible to obtain nearly any permutation of word pair data values over the entire active picture area by defining a particular flat color field in a noise-free environment. Certain of these permutations of word pair data values will produce the desired low-frequency effects.

#### 3 Checkfield data

- 3.1 Receiver equalizer testing is accomplished by producing a serial digital signal with maximum dc content. Applying the sequence 300h, 198h (C0.0, 66.0) continuously to the C and Y samples (respectively) during the active line will produce a signal of 19 consecutive high (low) states followed by one low (high) state in a repetitive manner, once the scrambler attains the required starting condition. Either polarity of the signal can be realized, indicated by the level of the 19 consecutive states. By producing approximately half of a field of continuous lines containing this sequence, the required scrambler starting condition will be realized on several lines, and this will result in the generation of the desired equalizer testing condition.

- 3.2 Receiver phase locked loop testing is accomplished by producing a serial digital signal with maximum low-frequency content and minimum high-frequency content (i.e., lowest frequency of level transitions). Applying the sequence 200h, 110h, (80.0, 44.0) continuously to the C and Y samples (respectively) during the active line will produce a signal of 20 consecutive high (low) states followed by 20 low (high) states in a repetitive manner, once the scrambler attains the required starting condition. By producing approximately half of a field of continuous lines containing this sequence, the required scrambler starting condition will be realized on several lines, and this will result in the generation of the desired phase locked loop testing condition.

- 3.3 Because the equalizer test works by producing a serial digital signal with a dc bias, steps must be taken to ensure that both polarities of dc bias are realized. To change the polarity of the dc bias from one frame to the next, the sum total of all the bits in all the data words in all the lines in a video field must be odd.

To ensure that the polarity of the bias can change often, a single Y sample data word in the signal is changed from 198h to 190h (a net change of 1 data bit), once every other frame. This causes the bias polarity to alternate at a frame rate regardless of whether the original frame bit sum is even or odd. The data word in which the value substitution is made is the first Y sample in the first active picture line of every other frame. The specific word and line for each signal format is listed in table 1 as the polarity control word.

3.4 The sequence 300h, 198h (C0.0, 66.0) and 200h, 110h (80.0, 44.0) applied to C and Y samples results in shades of purple and gray, respectively. Reversing the C and Y ordering for each of these two sequences results in lighter and darker shades of green, respectively. Table 1 illustrates one ordering of each of the two sequences, but either ordering of the data values for each sequence is permitted by this practice.

If the ordering described in 3.1 is reversed, then the polarity control word described in 3.3 is changed to 200h (80.0). The polarity control word in either case is located at the first Y sample in the first active picture line in the field(s) specified in 3.3.

# 4 Serial digital interface (SDI) checkfield

Distribution of data in the SDI checkfield is shown in Figure 13 for the signal standards referenced in annex A. Specific distributions of sample values are shown in Table 18. In each field, the line where the signal transitions from the equalizer test signal data pattern to the phase locked loop test signal data pattern is specified as a range of lines, rather than an a single specific line. Although the specific line selected within the specified range in not technically significant, the transition point should be consistent from frame to frame and from field to field (in the case of interlaced signal formats).

TABLE 18

# **SDI** checkfield sample values

|                                        |                                                         |                                                                               | 1125/60                                                                       |                                                 | 1250                                            | 0/50                                                                          |  |  |